Explore challenges and solutions in AI chip development

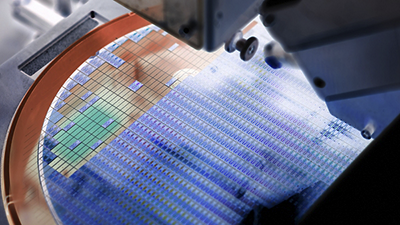

In the race to help chip designers get advanced, complex silicon chips to market quickly, it’s essential to holistically examine how various technology choices will impact silicon performance targets. Indeed, technology options such as new chip architectures and new materials that drive improvements in power, performance, and area (PPA) have become determining influencers in the scaling of process nodes.

How can you accelerate process node development while still meeting PPA targets?

This is where Design Technology Co-Optimization (DTCO) comes into play. DTCO solutions are geared to help both semiconductor technology and design teams by enabling the earlier exploration of technology choices and design styles and assessing their impact on silicon targets. An optimal approach considers things holistically, bringing together expertise across multiple domains, including atomistic simulation, TCAD and lithography modeling, foundation IP development, and custom and digital design methodologies to address the challenges. In this blog post, we will provide an overview of how early DTCO accelerates process exploration and, ultimately, supports the development of high-performing IP and chips.

A Head Start in Evaluating Your Technology Options

With CMOS scaling at advanced nodes, there’s now greater complexity than ever. This complexity, in turn, threatens project schedules and development costs. However, the process of evaluating different technology options requires time-consuming studies across specialized engineering teams. The analyses from these teams are based on a combination of silicon hardware data and scaling targets, and ultimately impact the process design kit (PDK), the common handoff between technology and design teams. Often, the feedback from these teams comes in too late to intercept the baseline technology definition.

Optimized DTCO solutions help technology teams shift left to explore technology optionality well before mature PDKs are available. Instead of waiting for design-level analysis based on traditional PDKs, for example, Synopsys DTCO capabilities allow much faster exploration of tradeoffs by leveraging simulation and physics-based models. This, in turn, drives a more efficient technology down-selection process that incorporates design-level feedback before PDKs are released for design analysis.

Accelerating New Technology Node Evaluation with Virtual PDKs for DTCO Exploration

For early DTCO exploration, virtual PDKs are critical to bridging the gaps between technology modeling and design implementation environments. While not as fully featured as a foundry-released PDK, these virtual PDKs can be generated quickly through simulation-based methods to enable design implementation and design analysis well before foundry PDKs are released to design teams.

These virtual PDKs incorporate the following critical capabilities when paired with Synopsys EDA products:

- Creation of compact models for circuit simulation

- Ability to run transistor-level parasitic extraction on custom designs

- Ability to run gate-level parasitic extraction on block-level designs

- Creation of technology files for synthesis, placement, and routing solutions

Our DTCO solutions enable generation of these virtual PDKs through automation from our technology development platform, thus enabling a seamless link between technology and design environments for the purpose of technology optionality studies. The following diagram illustrates our DTCO capabilities, which incorporate technology development and design exploration platforms to enable technology optionality and optimality.

Design-Level Evaluation on Technology Tradeoffs

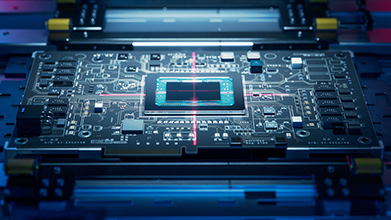

Whether you are exploring different material properties, device architectures, process integration schemes, device performance, or design rules, the ability to design and analyze IPs is crucial for true co-optimization. For example, if you were to explore the impact of contact-to-metal spacing design rules, the cell-level design may need to be re-designed, which could also change the custom or digital implementation techniques needed to design the entire system. This would, in turn, affect the silicon performance of the circuit or block.

With the myriad of process technology options and co-optimization needed with IP development and design implementation, Synopsys is building new capabilities into our products including Custom Compiler™, Fusion Compiler™, and DSO.ai™. We’re also focused on improving DTCO productivity with rich analytics solutions.

Continuing Moore’s Law Scaling

In summary, drawing on collective expertise from manufacturing, IP development, and chip design tools, Synopsys offers a comprehensive DTCO solution to help bring new process technologies to the market with accelerated productivity and velocity. We bring our deep experience working with a broad spectrum of partners, from manufacturing equipment vendors, process technology teams, IP development teams, and we accelerate technology scaling with innovate system-level DTCO solutions, while building in interoperability across our products to accelerate and increase the scale of DTCO analysis.